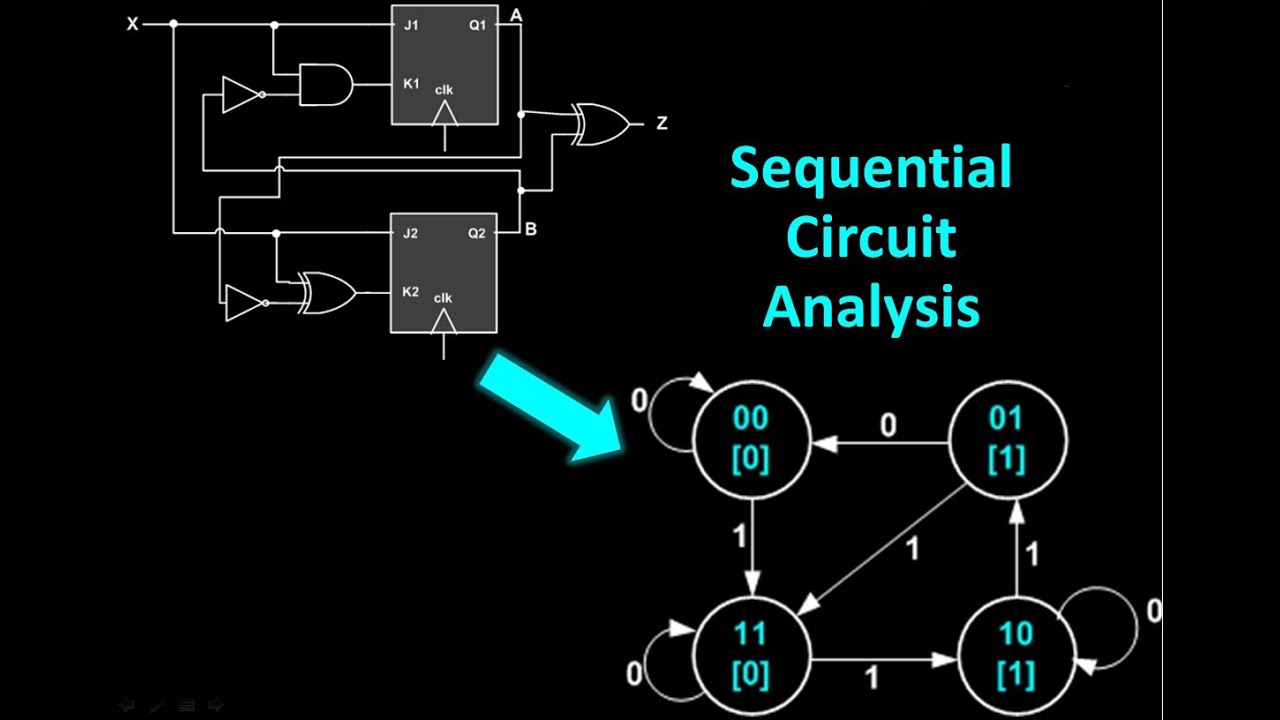

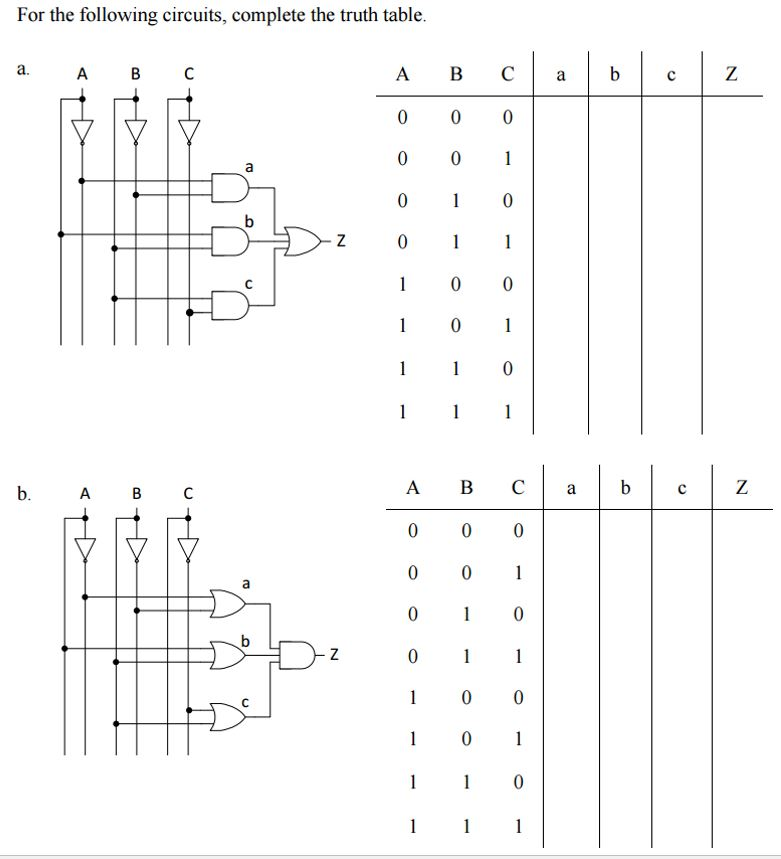

The state table for the circuit is listed below. X, and one output y and can be described algebraically by two input equations and an output The sequential circuit has two flip-flops A and B, one input The circuit can be specified by the characteristic equations: Similarly, the state equation for flip-flop B can be derived from the characteristic equation by substituting the values of J B and K B.:ī(t + 1) = x'B' + (A ⊕ x)'B = B'x' + ABx + A'Bx' The state equation provides the bit values for the column headed "Next State" for A in the state table. This gives us the state equation of A by substituting the values of J A, K AĪ(t + 1) = BA' + (Bx')'A = A'B + AB' + Ax The characteristic equations for the flip-flops are When J = K = 1, the next-state bit is the complement of the present-state bit. Value is the same as that of the present state.

When J = 0 and K = 0 there is no change of state and the next-state J and K inputs and the characteristic table of the JK flip-flop listed as: The next state of each flip-flop is evaluated from the corresponding The circuit can be specified by the flip-flop input equations: The expression specifies an odd function and is equal to 1 when only one variable is 1 or when all three variables are 1. The next-state values are obtained from the state equation A(t + 1) = A ⊕ x ⊕ y. The state table has one column for the present state of flip-flop 'A' two columns for the two inputs, and one column for the next state of A. No output equations are given, which implies that the output comes from the output

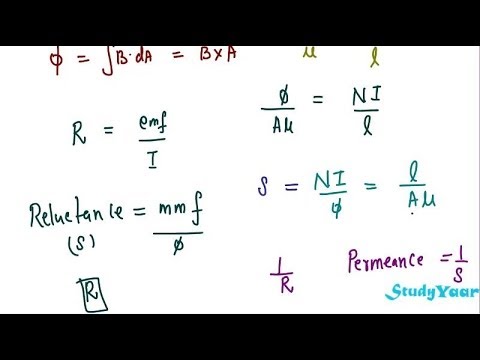

The x and y variables are the inputs to the circuit. The input equation of a D Flip-flop is given by D A = A ⊕ x ⊕ y. The value in D is transferred to Q with every positive-edge clock signal provided that R = 1. The clock at Clk is shown with an upward arrow to indicate that the flip-flop triggers on the positive edge of the clock. When R = 0, the output is set to 0 (independent of D and Clk). Two other connections from the reset input ensure that the S input of the third SR latch stays at logic 1 while the reset input is at 0 regardless of the values of D and Clk. When the reset input is 0 it forces output Q' to Stay at 1 which clears output Q to 0 thus resetting the flip-flop. It has an additional reset input connected to the three NAND gates. In general a sequential circuit with 'm' flip-flops and 'n' inputs needs 2 m+n rows in the state table.Ī circuit diagram of a Positive edge triggered D Flip-flop is shown as below. The table has four parts present state, next state, inputs and outputs. The time sequence of inputs, outputs, and flip-flop states can be enumerated in a state table (transition table). Of diagram a state is represented by a circle and the (clock-triggered)īy directed lines connecting the circles. The information available in a state table can be represented graphically in the form of a state diagram. Input equations (or excitation equations). The part of theĬircuit that generates the inputs to flip-flops is described algebraically by a set of Boolean functions called flip-flop Of Boolean functions called output equations. Of the combinational circuit that gene rates external outputs is described algebraically by a set The combinational circuit provide the information needed to draw the logic diagram of the sequential circuit.

The knowledge of the type of flip-flops and a list of the Boolean expressions of The direct inputs are useful for bringing all flip-flops in the system to a known starting state prior to the clocked operation. When power is turned on in a digital system, the state of the flip-flops is unknown. The input that clears the flip-flop to 0 is called clear or direct reset. The input that sets the flip-flop to 1 is called preset or direct Some flip-flops have asynchronous inputs that are used to force the flip-flop to a particular state independently of the clock

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed